A Service of

Leibniz-Informationszentrum Wirtschaft Leibniz Information Centre

Do, Wanglok; Equchi, Kei

## **Article**

Analysis of parallel connected Fibonacci switched capacitor converter

**Energy Reports**

## **Provided in Cooperation with:**

Elsevier

Suggested Citation: Do, Wanglok; Eguchi, Kei (2020): Analysis of parallel connected Fibonacci switched capacitor converter, Energy Reports, ISSN 2352-4847, Elsevier, Amsterdam, Vol. 6, Iss. 2, pp. 362-367,

https://doi.org/10.1016/j.egyr.2019.11.088

This Version is available at: https://hdl.handle.net/10419/243902

## Standard-Nutzungsbedingungen:

Die Dokumente auf EconStor dürfen zu eigenen wissenschaftlichen Zwecken und zum Privatgebrauch gespeichert und kopiert werden.

Sie dürfen die Dokumente nicht für öffentliche oder kommerzielle Zwecke vervielfältigen, öffentlich ausstellen, öffentlich zugänglich machen, vertreiben oder anderweitig nutzen.

Sofern die Verfasser die Dokumente unter Open-Content-Lizenzen (insbesondere CC-Lizenzen) zur Verfügung gestellt haben sollten, gelten abweichend von diesen Nutzungsbedingungen die in der dort genannten Lizenz gewährten Nutzungsrechte.

## Terms of use:

Documents in EconStor may be saved and copied for your personal and scholarly purposes.

You are not to copy documents for public or commercial purposes, to exhibit the documents publicly, to make them publicly available on the internet, or to distribute or otherwise use the documents in public.

If the documents have been made available under an Open Content Licence (especially Creative Commons Licences), you may exercise further usage rights as specified in the indicated licence.

NC ND https://creativecommons.org/licenses/by-nc-nd/4.0/

#### Available online at www.sciencedirect.com

## **ScienceDirect**

Energy Reports 6 (2020) 362-367

www.elsevier.com/locate/egyr

The 6th International Conference on Power and Energy Systems Engineering (CPESE 2019), September 20-23, 2019, Okinawa, Japan

# Analysis of parallel connected Fibonacci switched capacitor converter

Wanglok Do\*, Kei Eguchi

Department of Information Electronics, Fukuoka Institute of Technology, 3-30-1 Wajirohigashi, Higashi-ku, Fukuoka, 811-0295, Japan Received 7 October 2019; accepted 22 November 2019

#### Abstract

Switched capacitor converter (SCC) is a power converter without magnetic components. SCCs have been used in various portable electric products such as flash memories and energy harvesting systems. Conservative SCCs separately charge and discharge their output capacitors during one operating cycle. This operation reduces power efficiencies and increases output ripple voltages. To improve this problem, a parallel connected Fibonacci SCC (PFSCC) was suggested. The symmetric structure of the PFSCC can lead to its better output performance. As a preliminary stage to design a hardware and a controller for the PFSCC, this paper performs an analysis of the PFSCC to derive parameters such as its optimized capacitance and power stage transfer function. Also, simulations and comparisons with 4 different SCCs are conducted to verify its performance.

© 2019 Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

Peer-review under responsibility of the scientific committee of the 6th International Conference on Power and Energy Systems Engineering (CPESE 2019).

Keywords: Switched capacitor converter; Symmetric structure; Component optimizing; Circuit modeling

#### 1. Introduction

Switched capacitor converter (SCC) is a type of power converters. The SCC consists of semiconductor switches and capacitors without magnetic components such as inductors or transformers. This leads to reduction in the weight and size. Therefore, SCCs are usually used for portable devices like flash memories, energy harvesting systems and so on Forouzesh et al. [1]. There are several kinds of widely used SCCs such as Fibonacci type SCC (FSCC) [2], switched capacitor voltage multiplier (SCVM) [3], Dickson SCC [4] and series–parallel SCC [5]. These types of SCCs separately charge and discharge their output capacitors during their one operation cycle. This causes SCCs to increase the output ripple voltages and the capacitances of their output capacitors, and to reduce the power efficiencies as well. To improve those drawbacks, we suggested a parallel connected Fibonacci SCC (PFSCC) in previous study [6]. The symmetric structure of the PFSCC can improve its performance compared to the normal FSCC. However, the study [6] was not enough to implement a real hardware realization of the FSCC. The reason of this is because it was not performed in the past study to compare the PFSCC with more different types of SCCs in order to verify its performance and to analyze it with its switching frequency so as to design its controller. In

E-mail address: wanglok@bene.fit.ac.kr (W. Do).

https://doi.org/10.1016/j.egyr.2019.11.088

2352-4847/© 2019 Published by Elsevier Ltd. This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/).

Peer-review under responsibility of the scientific committee of the 6th International Conference on Power and Energy Systems Engineering (CPESE 2019).

<sup>\*</sup> Corresponding author.

this paper, a comparative study with other SCCs and a theoretical analysis of the PFSCC in its stable state are implemented as a preliminary study to design a hardware and a controller for the PFSCC. To analyze the PFSCC, four-terminal equivalent (FE) model [6] is utilized to derive its conversion ratio and output impedance. Although the modeling of slow and fast switching limit impedance in the study [7] is more accurate than the FE model, there is an assumption in the modeling that a targeted SCC has only 50% duty ratio of its switch-on and off time for its switching period. Unlike that, it is possible to regulate the duty ratio in the FE model. In the study [8], capacitor ampere-second balance transient calculation (CASBTC) modeling method is even more precise than the model of Seeman and Sanders [7] but CASBTS is performed based on differential equations with every single capacitor capacitance in the targeted converter. This requires more tedious and complex expressions for parameters of any SCCs when they are constructed with tens capacitors and switches. In this paper, the PFSCC is analyzed based on charged and discharged charge amounts in capacitors of the PFSCC during one operating cycle. This method leads to concise expressions compared with two abovementioned analysis methods. Also, sizing capacitance of capacitors in the PFSCC and deriving power stage transfer function of it can be performed. Concretely, conversion ratio, output impedance, capacitance sizing and power stage transfer function of the PFSCC are theoretically derived by using two analysis methods of the FE model and the charge amount calculation.

The remainder of this paper is divided as follows. Section 2 introduces the circuit configuration of the PFSCC. In Section 3, the PFSCC is theoretically analyzed to derive parameters. Section 4 describes simulations and comparisons with 4 different SCCs. In Section 5, we discuss a conclusion and a future study.

## 2. Converter topology

#### 2.1. PFSCC

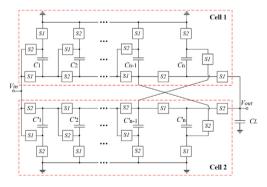

Fig. 1 illustrates a PFSCC consisting of two normal FSCCs connected in parallel. This parallel structure can continuously provide boosted voltages to the output capacitor, while a normal FSCC charges and discharges it at each half operating cycle, respectively. Switches of the PFSCC are operated by a switching rule. The switching rule is that S1 switches are on and S2 switches are off when the PFSCC is in state-1, and S1 switches are off and S2 switches are on when it is in state-2. This operation and structure reduce the capacitance of the output capacitor than that of the normal FSCC, which also indicates that it helps the PFSCC generate its output voltage with smaller output ripple voltages than that of the normal one [6].

Fig. 1. Circuit configuration of the PFSCC.

#### 2.2. The operation of PFSCC

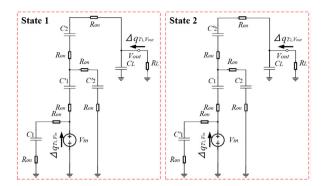

The PFSCC has two IECs (instantaneous equivalent circuits) during one operating cycle. Fig. 2 illustrates the IECs at the conversion ratio of 4 times. In the switching rule, nth capacitor in each stage of each cell is charged up to the sum of (n-1)th and (n-2)th capacitors' voltage, where n > 2. When n = 1, 2, the first and second capacitors (C1 and C2, and C'1 and C'2) are charged up to 1 and 2 times  $V_{in}$ , respectively. In both cases, the nth capacitors are connected in series so that the PFSCC can generate 2 times higher output voltage than that of the normal FSCC.

Fig. 2. IECs of the PFSCC at the conversion ratio of 4 times.

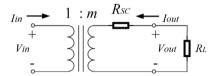

Fig. 3. The four terminal equivalent model.

## 3. Theoretical analysis and capacitor optimization

#### 3.1. FE model

The PFSCC is analyzed based on the four-terminal equivalent circuit model in Fig. 3. In Fig. 3,  $I_{in}$ ,  $I_{out}$ ,  $V_{in}$ ,  $V_{out}$ , and m are the input and output average current, the input and output average voltage and the conversion ratio of a modeled converter, respectively.  $R_{SC}$  and  $R_L$  are the switched capacitor resistor (output resistor or impedance) and the load resistor of it. This modeling is performed with the conversion ratio of 4 times.

During operating states (state-1 and 2), charged and discharged charge amounts of all capacitors are the same as shown as (1).

$$\Delta q_{T1}^{y} = -\Delta q_{T2}^{y}, \ \Delta k_{T1}^{y} = -\Delta k_{T2}^{y}, \tag{1}$$

where  $\Delta q^y_{T1}$ ,  $\Delta k^y_{T1}$ ,  $\Delta q^y_{T2}$  and  $\Delta k^y_{T2}$  ( $1 \le y \le n$ ) are the charge amounts of the yth capacitor in yth stage of cell-1 and 2 at state-1 and 2, respectively.

By setting the 50% duty ratio of each operating state, the operating period, T, of the PFSCC is given as (2).

$$T = \sum_{i=1}^{2} Ti$$

and  $T1 = T2 = T/2$ . (2)

By applying KCL to IECs in Fig. 2, the relations of the input and output source and capacitors of PFSCC are given as (3) at state-1 and 2, respectively.

$$\Delta q_{T1,V_{in}} = \Delta q_{T1}^1 - \Delta k_{T1}^1, \ \Delta q_{T1,V_{out}} = \Delta q_{T1}^L + \Delta q_{T1}^2, \ \Delta q_{T2,V_{in}} = \Delta k_{T2}^1 - \Delta q_{T2}^1, \ \Delta q_{T2,V_{out}} = \Delta q_{T2}^L - \Delta q_{T2}^2,$$

$$(3)$$

where  $\Delta q_{Ti,Vin}$  and  $\Delta q_{Ti,Vout}$  are the charge amounts of input and output source and  $\Delta q^L_{Ti}$  is the charge amount of the output capacitor at state-1 and 2, (i = 1 and 2).

By substituting (1) into (3), the relation of average input and output current for one operating cycle,  $I_{in}$  and  $I_{out}$ , are given as (4). Therefore, the conversion ratio of PFSCC, m, is 4.

$$I_{in} = -4I_{out}. (4)$$

To calculate  $R_{SC}$ , the consumed energy during one operating cycle is given as (5). Because it has the symmetric IECs, the consumed energy,  $W_{T1}$  and  $W_{T2}$ , are the same and  $W_T$  is obtained. From this,  $R_{SC}$  is derived as  $16R_{on}$ .

$$W_{T1} = W_{T2} = \{ (4R_{on})/T1 \} \left( \Delta q_{T1}^{out} \right)^2, \ W_T = \{ (16R_{on})/T \} \left( \Delta q_{V_{out}} \right)^2.$$

(5)

By using derived parameters, the output voltage and efficiency,  $\eta$ , can be calculated as (6).

$$V_{out} = \eta V_{in} = \{R_{SC}/(R_L + R_{SC})\} V_{in}. \tag{6}$$

## 3.2. Capacitor optimization

To determine sizes of capacitors, we assume that all charged energy in flying capacitors can be transferred into the output capacitor without any loss. With this assumption, the difference between the charged and discharged charge amounts in flying capacitors should be the same as the total charge amount of the output capacitor during one operation cycle, which is expressed as (7).

$$C_f\left(\frac{3}{2}\right)V_{out} - 2C_f\left(V_{out} - V_{in}\right) = C_L \Delta V_{out},\tag{7}$$

where  $\Delta V_{out}$  is the ripple voltage of the output and  $C_f$  and  $C_L$  are the capacitances of the flying capacitors and the output capacitor.

If the ripple voltage is much smaller than the output voltage, the transferred energy,  $E_{transfer}$ , into the output capacitor can be expressed as (8).  $E_{transfer}$  should be the same as the consumed energy by the load.

$$E_{transfer} = C_L V_{out} \Delta V_{out} = \frac{(V_{out})^2}{R_L} \cdot \frac{1}{f}.$$

(8)

where f is the frequency of the operating cycle.

By combining (7) and (8), the capacitances of the flying capacitors and the output capacitor can be optimized as (9) and, respectively.

$$C_f = V_{out} / \{R_L \cdot f \cdot (2V_{in} - V_{out})\}, C_L = V_{out} / (R_L \cdot f \cdot \Delta V_{out})$$

$$(9)$$

#### 3.3. Power stage transfer function

With consideration of a digital control, the PFSCC is modeled in z-domain to obtain its power stage transfer function. First, At (n-1)T, the total charged charges in all capacitors,  $Q_{charge}$ , are derived and expressed as (10).

$$Q_{charge}((n-1)T) = \left(\frac{3}{2}C_f + C_L\right)V_{out}((n-1)T).$$

(10)

At nT, the discharged charges in all capacitors,  $Q_{disch}$ , are calculated as (11)

$$Q_{disch}(nT) = 2C_f(V_{out}(nT) - V_{in}(nT) + C_L V_{out}(nT)).$$

(11)

The output current during one operating cycle, T, should be equal to the difference between the charged and discharged charges divided by T, which is given as (12).

$$\frac{\left(Q_{charge}\left(\left(n-1\right)T\right)-Q_{disch}\left(nT\right)\right)}{T}=\frac{\left(V_{out}\left(\left(n-1\right)T\right)+V_{out}\left(nT\right)\right)}{R_{L}}.\tag{12}$$

By substituting (10) and (11) into (12) and transferring it on z-domain, the power stage transfer function of the PFSCC is derived as (13).

$$\frac{V_{out}}{V_{in}} = \frac{2C_f}{\left[\left\{-\frac{3}{2}C_f - 2C_L + (T/R_L)\right\} + \left\{2C_f + 2C_L + (T/R_L)\right\}\right]}z^{-1}.$$

(13)

## 4. Simulation and comparison

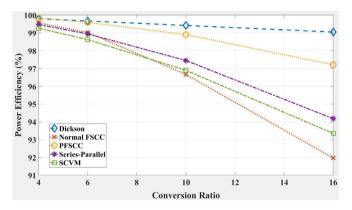

To compare the PFSCC with 4 SCCs (normal Fibonacci [2], Dickson [4], SCVM [3] and series–parallel type [5]), the converters are simulated with the conditions as follows:  $R_{on} = 0.1 \Omega$ ,  $R_L = 1 \text{ k}\Omega$ ,  $C = 10 \mu\text{F}$ , D = 0.5,  $V_{in} = 10 \text{ V}$ , Conversion ratio = 4, 6, 10, 16.

As Fig. 4 shows, the PFSCC and Dickson SCC are the SCCs with the highest power efficiencies at the conversion ratio of 4 and 6. At conversion ratio of 10 and 16, the PFSCC has the second highest power efficiencies among others.

Fig. 4. Power efficiencies at different conversion ratios.

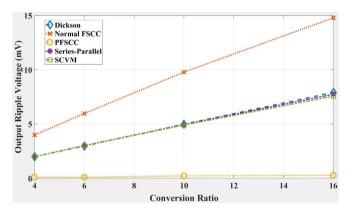

Fig. 5 demonstrates the output ripple voltage at different conversion ratios. The converter with lowest output ripple voltage is the PFSCC. This is because it has the symmetrical structure.

Fig. 5. Output ripple voltage at different conversion ratios.

#### 5. Conclusion

This paper has analyzed the PFSCC. From the analysis, we derive the parameters as follows: output voltage, power efficiency, optimized capacitances of capacitors and power stage transfer function. It is confirmed by the simulations and comparisons that the PFSCC has high power efficiency and low output ripple voltages. If a target system requires an SCC with high power efficiency and low ripple voltage, the PFSCC can be a solution.

For a future study, the obtained parameters will be utilized to design a digital control and a hardware of the PFSCC.

#### References

[1] Forouzesh M, Siwakoti YP, Gorji SA, Blaabjerg F, Lehman B. Step up dc-dc converters: a comprehensive review of voltage-boosting techniques, topologies, and applications. IEEE Trans Power Electron 2017;32(12):9143–78.

- [2] Harada I, Ueno F, Inoue T, Oota I. Characteristics analysis of fibonacci type sc transformer. Proc IEICE Trans Fundam Electron Commun Comput Sci 1992;75(6):655–62.

- [3] Chang Y-H. Variable-conversion-ratio switched-capacitor-voltage multiplier/ divider dc-dc converter. Proc IEEE Trans Circuits Syst I 2011;58(8):1944–57.

- [4] Dickson JF. On-chip high-voltage generation in mos integrated circuits using an improved voltage multiplier technique. IEEE J Solid-State Circuits 1976;11(3):374–8.

- [5] Mak O-C, Wong Y-C, Ioinovici A. Step-up dc power supply based on a switched-capacitor circuit. IEEE Trans Ind Electron 1995;42(1):90-7.

- [6] Do W, Eguchi K. Parallel-connected type of fibonacci sequence switched capacitor dc-dc converter. In: Proc. of the 5th IIAE international conference on intelligent systems and image processing. 2017. 364-370.

- [7] Seeman MD, Sanders SR. Analysis and optimization of switched-capacitor dc-dc power converters. IEEE Comput Power Electron Workshop 2006;021:6–224.

- [8] Wu B, Yang L, Zhang X, Smedley KM, Li G. Modeling and analysis of variable frequency one-cycle control on high-power switched-capacitor converters. IEEE Trans Power Electron 2018;33(6):5465–75.